이번 포스팅은 CMOS VLSI design을 공부한 내용이며,

깊게 들어간다기보다는 VLSI design에 대한 전반적인 내용을 다룹니다.

각 소주제에 관한 세부적인 내용은 따로 포스팅할 예정입니다.

Introduction

이번 챕터는 VLSI design 과정 중 test에 관련된 내용인데,

일반적으로 testing 단계는 chip 생산 과정에서 비용이 많이 드는 과정 중 하나입니다.

기술의 발전은 회로의 complexity (복잡성)의 증가로 이어지며,

결과적으로 Testing 비용은 complexity에 비례하여 증가하게 됩니다.

일반적인 testing 과정은 다음과 같습니다.

- Logic verification

- Tape-out 이전에 수행되며, realistic simulation을 통해 수행

- Silicon debug

- Chip 제조 이후, probe를 사용해서 직접 측정

- Manufacturing test

- 가장 마지막 단계로써 chip 내의 모든 transistor (tr.), gate 등이 제대로 동작하는지 확인

Logic verification

앞서 이야기 한 logic verification에 대해서 조금 더 자세히 알아보면,

이 testing 과정은 여러 단계에 걸쳐 회로의 functionality를 확인합니다.

각 단계 사이에는 check points가 존재하며, 이들을 만족해야 logic verification을 통과합니다.

Logic verification 과정은 앞서 이야기한 것처럼 realistic simulation을 통해 수행되기 때문에 구체적인 연산을 포함합니다. 이는 곧 runtime의 증가로 이어지는데, 이를 최소화하기 위해 hierarchy (계층적) 구조를 사용합니다.

그렇게 다음 그림과 같이 여러 단계에 걸쳐 check points를 확인합니다.

각 단계에 대한 설명은 다음과 같습니다.

- Beavioral specification: 회로나 시스템의 동작을 낮은 수준으로 기술

- RTL specification: VHDL 또는 verilog 수준으로 회로의 세부 사항과 register, gate 등을 표현

- Structural specification: 각 요소들 간에 연결 방식을 gate-level netlist로 표현

- Physical specification: 공정에 필요한 모든 세부 사항을 포함

이러한 각 단계들을 지나면서 check points를 확인하고 설계에 이상 여부를 판단합니다.

Silicon debug

Silicon debug는 다양한 probe나 장비를 사용해서 생산된 chip을 debugging 하는 과정입니다.

가장 일반적으로는 pico-probe 장비를 사용해서 검증을 위해 설계된 probe point를 측정합니다.

다음 그림의 probe는 10μm × 10μm크기까지 측정할 수 있는 pico-probe입니다.

이처럼 pico-probe는 물리적인 탐침을 통해 chip의 결함을 관측합니다.

Laser voltage probe (LVP)라는 장비의 경우, photo voltaic effect를 통한 전압 유도를 통해 간접적으로 탐침을 수행합니다.

이는 물리적으로 탐침 하기 않기 때문에 complexity가 높은 chip이나 손상되기 쉬운 chip에 사용됩니다.

또한 다수의 points를 동시에 또는 빠른 속도로 연속적으로 측정할 수 있기에 testing time을 줄일 수 있습니다.

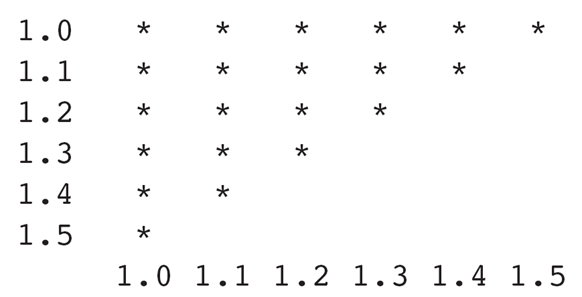

Shmoo plot은 다양한 환경에서 chip이 제대로 동작하는 지를 알아보기 쉽게 표현하기 위한 방법입니다.

아래 표는 x축: clock frequency, y축: voltage인 Shmoo plot을 보이고 있습니다.

이 plot에서는 freq.와 voltage가 비례 관계에 있음으로 잘 동작하는 chip인 것을 알 수 있습니다.

이러한 표현 방식은 통해 회로의 결함이 어떠한 경향을 보이는지 직관적으로 보여주며, testing 시에 다양한 관점(x, y)에서의 결함을 빠르게 파악할 수 있도록 도와줍니다.

Manufacturing test

이 과정은 제품이 시장에 출시되기 전에 품질과 기능을 확인하는 단계입니다.

일반적으로 산업에서의 target defect rate는 0.035% ~ 0.1%으로 설정합니다.

검출되는 결함의 예시는 다음과 같습니다.

- Shelving: 서로 다른 패턴이 접촉

- Bridging defect: 서로 다른 전도체들 사이에 의도치 않은 전기적 연결이 발생

- Open defect: 회로의 연결이 끊어지거나 전기적으로 연결되지 않을 경우

- Infant mortality: 고장률이 비정상적으로 높은 경우. 그림은 via2의 구조가 느슨한 상황

- Patterning defect: 회로 패턴이 제대로 형성되지 않은 경우

- Spot defect: 소자 표면에 있는 작은 불량 영역 발생

- Open at contact: 패턴 누락으로 인해 회로의 연결이 제대로 되지 않은 경우

사실, 외관 검사, functional test, parametric test, stress test, burn-in test 등 여러 과정이 있지만, 이러한 세부적인 내용을 다루면 너무 방대해져서 따로 주제를 잡고 포스팅하겠습니다.

Manufacturing test에서 사용되는 방법 중 일반적인 것은 fault model입니다.

이것은 결함 발생 원인 및 이에 따른 회로 상의 효과를 모델링하여, 회로를 test 하는 방법입니다.

그중에서 stuck-at model은 ploy gate (그림의 수직선)가 0 또는 1로 고착되는 경우를 모델링합니다.

다음은 이러한 fault model의 예시입니다.

왼쪽 그림은 회로가 0과 1로 고착된 경우이고, 오른쪽 그림은 metal이 서로 연결된 경우입니다.

이러한 결함은 설계자와 의도와 다르게 완전히 다른 회로를 생성하게 됩니다.

결국, 이러한 model을 적용하기 위해서는 검증자가 원하는 위치의 node를 원하는 상태로 변경할 수 있어야 하며, 원하는 위치의 상태를 출력으로써 받아올 수 있어야 합니다.

이러한 관점을 controllability와 observability라고 합니다.

Controllabilty는 입력에서부터 얼마나 깊은 수준의 node를 control 할 수 있는 지를 나타내며,

observability는 출력에서부터 얼마나 깊은 수준의 node 상태를 관측 가능 한지를 나타낸다.

Scan design

Scan은 앞서 이야기한 controllability와 observability를 확실하게 만족시키기 위한 방법입니다.

Scan은 flip-flop 앞에 MUX가 붙은 scan register로 구성되며, MUX를 사용해서 normal mode와 scan mode를 설정합니다.

Normal mode에서는 단순한 D flip-flop의 동작을 수행하며, scan mode에서는 testing을 위한 회로로 동작합니다.

Scan design에서는 위의 scan register를 연속적으로 연결한 구조인 scan chain을 형성하도록 설계합니다.

다음 그림과 같이 flip-flop의 출력 Q는 다음 scan register의 SI 단자로 들어가게 됩니다.

이러한 구조를 통해서 그림처럼 scan-in에서 데이터가 입력되면, 이전에 있던 데이터가 다음 scan register로 옮겨가는 shift register를 구현합니다.

Test pattern을 각 register로 전송할 수 있으며, 측정 결과를 scan-out에서 serial로 읽어올 수 있습니다.

사실 이 scan chain의 구조는 data를 loading 또는 un-loading하는 과정에서 runtime을 많이 소모합니다.

모든 scan register가 하나로 엮여있다면 특정 회로에 대한 testing만 진행하려고 해도 다른 회로까지 사용됩니다.

이러한 문제를 해결하기 위한 방법이 parallel scan입니다.

이 회로는 원하는 부분에 대한 testing만을 수행할 수 있으며, 여러 scan chain에 대한 testing도 동시에 수행할 수 있습니다.

따라서, 앞서 발생한 testing runtime 문제를 해소할 수 있습니다.

이번 포스팅에서는 VLSI design 과정 중 test를 다뤘습니다.

여기서의 test는 제조 공정을 마치고 결함을 검출하는 과정에 중점이 맞춰진 느낌이고,

교재를 기반으로 공부한 내용을 정리한 것이어서 세세한 방법과 설명은 많이 부족합니다.

이런 부분들은 시간이 허락하는 대로 최대한 공부해서 포스팅해보겠습니다.

출처

Neil Weste and David Harris. 2010. CMOS VLSI Design: A Circuits and Systems Perspective (4th. ed.). Addison-Wesley Publishing Company, USA.

'VLSI Design' 카테고리의 다른 글

| Multi-Cycle Path(MCP) (0) | 2024.05.16 |

|---|