Multi-Cycle Path(MCP)

MCP는 flop사이의 경로로, flop사이의 combination logic delay가 하나 이상의 clock cycle을 취할 수 있도록 허용합니다. 예로 큰 지연이 있는 timing path는 source에서 대상까지 propagate하기 위해 multiple cycle이 허용되도록 설계됩니다.

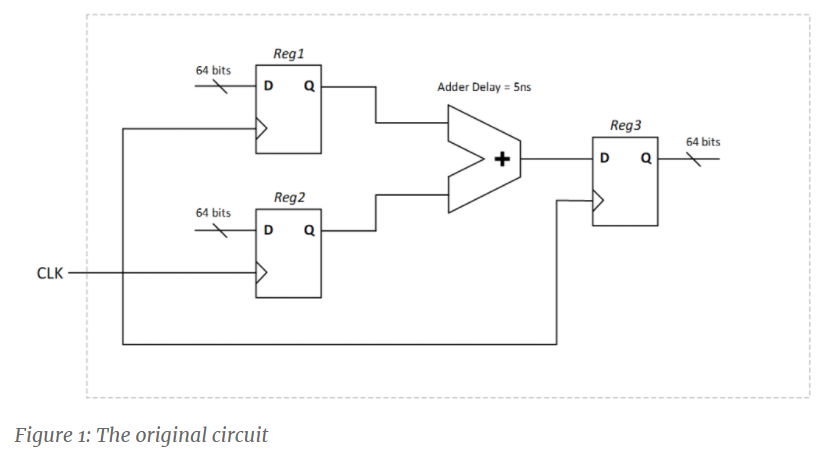

그림 1과 같은 design에 하나의 clock(2ns)만 있고 2개의 bus에 64bit 추가를 수행하는 예가 있습니다. 가산기의 input bus와 output bus가 등록됩니다. 가산기의 최대 지연은 약 5ns로 추정되며, 레지스터 clock의 주기는 2ns입니다. 가산기는 clock의 time period 이상으로 delay되기 때문에 one clock period 내에서 timing을 맞출 수 없습니다.

회로가 올바르게 작동하기 위해 multi-cycle design 방식이 구현되었습니다. 모든 레지스터에 001이 preload되고, output에서 input으로 feedback loop가 있는 3bit shift register에 의해 제어되는 공통으로 연결된 활성화 bit가 있습니다. 이로 인해 enable 신호가 3 cycle마다 high가 됩니다.

단순히 "create_clock -period 2[get_ports CLK]" constraint를 적용하면 synthesis tool은 가산기가 setup check timing closure를 위한 3개의 cycle을 가지고 있는다는 것을 이해하기 위해 enable control logic을 분석하지 않습니다(Tool이 dynamic logic simulation을 수행하지 않기 때문). 따라서 가산기 logic을 최적화하여 1 clock cycle period 내에서 setup time을 닫으려고 합니다. 이는 불가능하며, 불필요합니다.

따라서 input register와 output register 사이에 MCP를 추가해야합니다. 이는 set_multicycle_path command과 3만큼의 setup value(3 period에 해당)를 지정하여 수행되며, 다음과 같이 Reg1&Reg2에서 시작하여 Reg3에서 끝나는 path에 적용됩니다.

set_multicycle_path -setup 3 -from{Reg1[*]Reg[*]} -to Reg3[*]

(Note : Reg의 모든 bit(64)를 고려하기 위해 [*]가 추가됩니다.)

기본적으로(MCP constraint없이), setup check는 source clock edge에서 대상의 다음 clock edge까지 측정되고. hold check는 source clock edge에서 대상의 동일한 clock edge까지 측정됩니다. 즉, setup timing이 수행되는 동일한 clock period에서 hold timing analysis가 수행된다고 말할 수 있습니다.

N의 MCP setup이 적용되었다고 가정했을때, 명시적으로 hold MCP가 설정되지 않은 경우, default hold check는 대상 clock의 (N-1) 번째 edge에서 수행됩니다. 이 hold requirement를 충족하기 위해, synthesis tool에 의해 추가 buffer가 추가되어 불필요하게 area, power 등이 증가합니다. 일반적으로 setup을 대상 clock의 N번째 edge로 이동하고, hold check는 대상 clock의 0번째 edge에 있어야 합니다. 이렇게 하려면 setup 및 hold MCP constraint를 모두 지정해야 합니다.

앞서 이야기한 예에서 setup capture clock edge를 3th cycle(6ns)로 이동했으므로 hold timing analysis는 setup capture edge와 동일한 cycle(or period) 내에 있는 4ns에서 synthesis tool에 의해 수행됩니다. 그러나 이것은 가장 빠른 operation condition에서 64bit 가산기를 통한 가장 빠른 path가 (4ns + Reg1 or Reg2의 유지 시간)보다 느려야 한다는 것을 의미하며, register가 활성화되었기 때문에 필요하지 않습니다. 따라서, data가 0ns와 6ns 사이의 이전 clock edge 중 하나에 올바르게 도착한다면, hold violation으로 인한 metastability 가능성을 우려하지 않습니다. 그래서 우리는 lunch edge와 같은 edge에서 hold check를 수행하기를 원합니다. Hold check를 2 clock cycle만큼 되돌리려면 다음을 사용합니다.

set_multicycle_path -hold 2 -from{Reg[*]Reg2[*]} -to Reg3[*]

Hold option의 default는 0이며, 이는 hold check가 setup check와 동일한 cycle 내에서 수행되거나 setup capture clock edge가 발생하기 전에 one clock cycle 내에서 수행됨을 의미합니다. 따라서 timing engine tool로 정확한 analysis를 원할 경우, setup 및 hold MCP constraint를 모두 지정하는 것입니다.

출처 : https://vlsitutorials.com/constraining-multi-cycle-path-in-synthesis/